Description

- Type : Transmetteur LVDS (Low-Voltage Differential Signaling) programmable.

- Alimentation : 3,0 à 3,6 V (nominal 3,3 V).

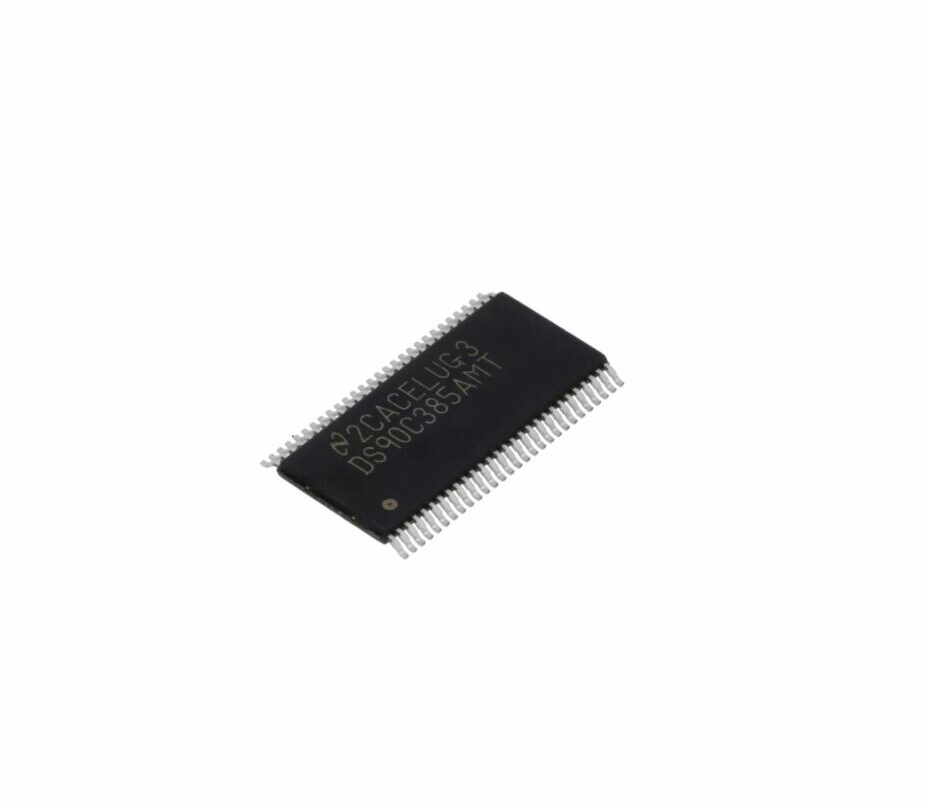

- Package : 56 broches TSSOP.

- Plage de température : de –10 °C à +70 °C.

- Fréquence d’horloge (“shift clock”) : support de 18 à 87,5 MHz.

- Support du Spread Spectrum Clocking : modulation jusqu’à 100 kHz avec déviation ±2,5 % (centre) ou –5 % (down spread).

- Détection d’absence d’horloge (“Input Clock Detection”) : quand l’horloge d’entrée est manquante et /PD est logique haut, toutes les paires LVDS sont tirées à l’état bas.

- Consommation :

- Typique : < 147 mW à 87,5 MHz (“grayscale”).

- Mode “power-down” : < 60 µW typique.

- Débit : jusqu’à 2,45 Gbps (embarqué sur les quatre canaux LVDS).

- Bande passante : jusqu’à 306,25 Mo/s (avec l’horloge à 87,5 MHz).

- Amplitude du signal LVDS : ~ 345 mV typique, pour limiter les EMI.

- PLL intégrée : pas de composants externes nécessaires.

- Standard LVDS : conforme à TIA / EIA-644.

- Interface : convertit 28 bits de données LVCMOS / LVTTL en 4 flux LVDS + un lien d’horloge LVDS.

- Mode “Strobe” (échantillonnage des données) : programmable pour bord montant (rising) ou descendant (falling) via une broche dédiée.

- ESD (tolérance décharge électrostatique) : 7 kV (HBM).

- Dissipation thermique maximale (à 25 °C) : 1,63 W pour le boîtier TSSOP