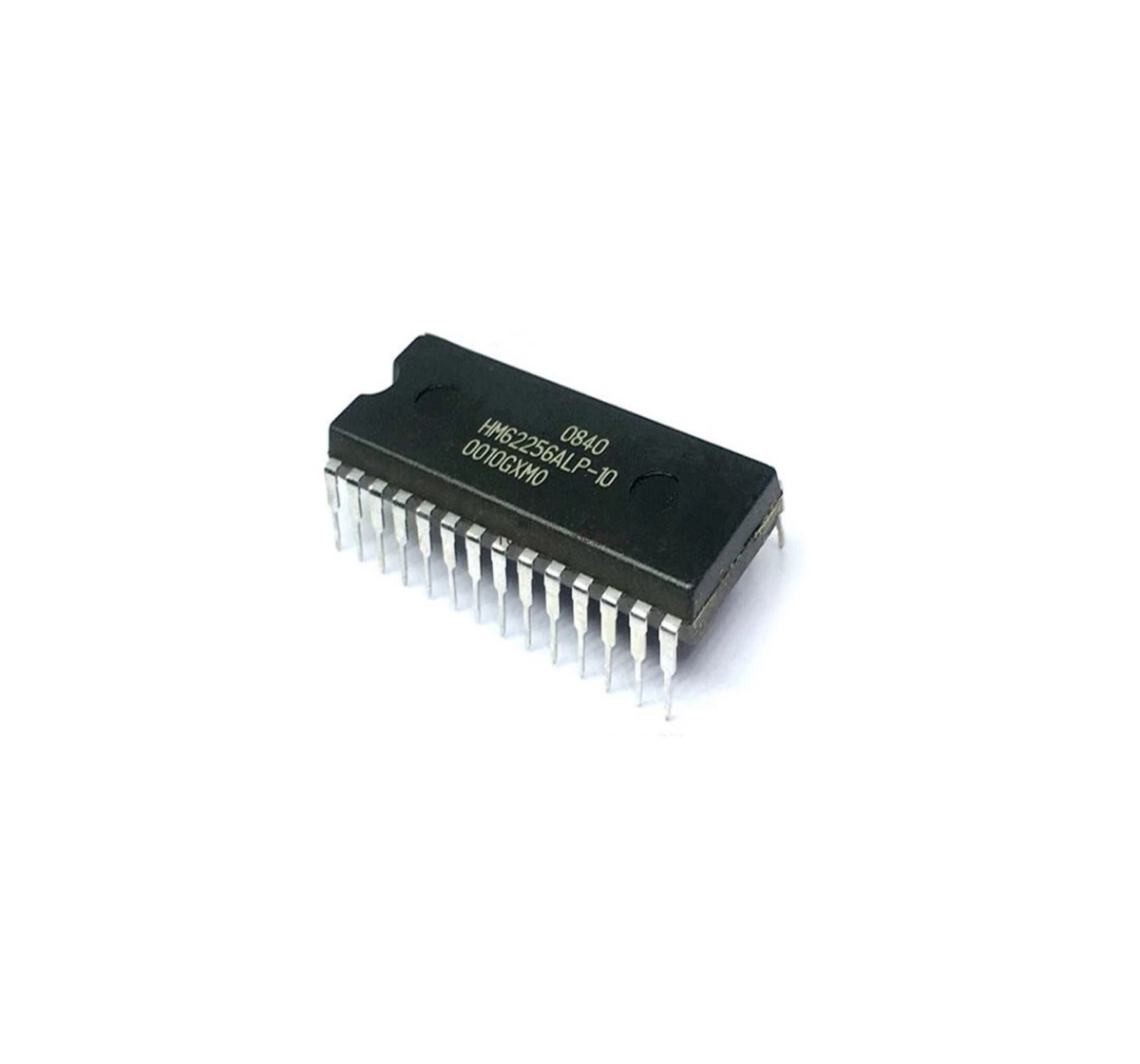

Description

circuit HM62256ALP‑10 de Hitachi, une mémoire SRAM CMOS statique haute vitesse

- Capacité : 32 768 mots × 8 bits = 256 kbit

- Topologie : SRAM statique — mémoire sans rafraîchissement, accès aléatoires

- Boîtier : DIP‑28

- Tension d’alimentation (Vₛᵤₚₚ) : 5 V nominal (4,5–5,5 V)

- Mode veille (standby) : typiquement 5 µW (versions L/L‑SL) ou ~~200 µW selon condition

- Consommation en fonctionnement : ≈ 40 mW à 1 MHz

- Temps d’accès : 100 ns (version ‑10)

- Cycle acc/lecture égal : accès et cycle synchronisés, performances fiables

- Bus :

- Adresses : A0–A14 (15 lignes) pour un espace de 32 K adresses

- Données : D0–D7, bi-directionnel, entrée/sortie tri-état

- Signaux de contrôle :

- CE (Chip Enable) : active/mets la puce en veille

- OE (Output Enable) : active la sortie

- WE (Write Enable) : commande d’écriture

- Compatibilité TTL : toutes les entrées/sorties sont TTL-compatibles